Shaping the future of cloud AI with silicon photonics

Silicon photonics is transforming Cloud AI with high-speed, energy-efficient data movement. Soitec’s Photonics-SOI engineered substrates are key enablers, enhancing performance, scalability, and integration for next-gen AI infrastructures.

By René Jonker, Executive Vice President of Edge & Cloud AI Division, Soitec

Cloud-based AI has become a cornerstone of digital transformation. From natural language processing to computer vision, large-scale AI models hosted in hyperscale datacentres are delivering unprecedented value across a wide array of industries. However, as these models grow in complexity and size, the infrastructure supporting them is approaching critical bottlenecks.

Two dominant challenges define the current landscape: bandwidth limitations and excessive power consumption. Training and deploying AI models involves massive data exchange between GPUs, CPUs, memory, and storage. Traditional electrical interconnects are struggling to scale bandwidth to the necessary levels to support frontier models without increasing latency.

Those same interconnects in modern AI datacentres currently consume over 30 percent of total system power. As AI usage continues to grow, this number is projected to rise, threatening sustainability goals as well as the economic viability of operating AI models. Table 1 shows the energy consumption of large language models like ChatGPT based on carbon emissions associated with electricity production. This emission is equivalent to driving an average passenger vehicle for approximately 2,190,000 km (GPT-3), 3,650,000 km (GPT-4), or 7,300,000 km (GPT-5), using the EPA’s estimate of 0.25 kg CO2 per km.

These challenges underscore an urgent need for a new paradigm in data movement – one that combines speed, energy efficiency, and scalability. And this is where silicon photonics comes in, moving data at high speeds within and between chips, using silicon as the optical medium. Compared with traditional copper-based electrical connections, photonic interconnects can transmit data with significantly less energy loss and higher bandwidth, all while leveraging the mature silicon CMOS fabrication ecosystem.

Table 1. Comparison of energy consumption of AI models (Source: Baeldung).

Current pluggable optics achieve data rates exceeding 800G for scale-out networking, with roadmap projections reaching several terabits per second in the coming years. Such pluggable optics consume roughly 15-20 pJ/bit. As the compute and data rate requirements grow along with the ever-increasing model sizes, new architectures will be required to further improve the energy efficiency of just moving data within the compute clusters.

This is where co-packaged optics (CPO) comes in. This technology integrates optical engines close to, or alongside, the ASIC within the same package. This shortens the length of high-speed electrical traces and thus reduces power loss and signal degradation. Such implementations reduce energy consumed to 5-7 pJ/bit, while future advancements in semiconductor packaging technology will likely bring further improvements to cross the sub-1 pJ/bit barrier.

From a system point of view, bringing the optics closer to the ASIC – as represented in Figure 2 - helps to shrink the system footprint, offering higher bandwidth density and enabling scalable designs for larger AI clusters. Additionally, even if the optics in CPO devices are within the same module as the electronics, they are not fully integrated on the same silicon die. This means there is still an element of modularity, facilitating easier future upgrades without requiring an entire system redesign.

Soitec’s role in the ecosystem

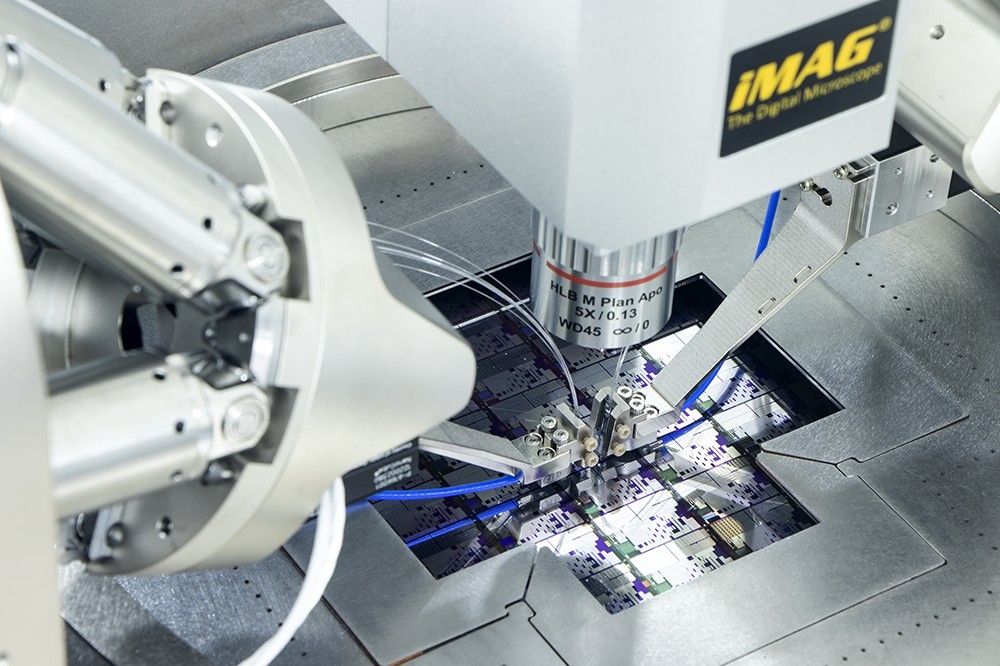

The success of silicon photonics in cloud AI does not rest on a single player, but rather on a collaborative ecosystem, connected by strategic partnerships across the value chain. The key players at the design and fabrication stage include foundries for scalable chip production as well as design houses and research and technology organisations for innovative optical IP blocks. Once the chip is made, it requires packaging experts for high-precision alignment and thermal management, and system integrators for AI-scale deployment.

Soitec’s substrates are at the heart of this ecosystem, enabling wafer-level integration and performance consistency across global photonics fabs, and thus facilitating the large-scale adoption of silicon photonics. In particular, the Smart Cut technology pioneered by Soitec and CEA-Leti offers an unmatched method for producing substrates of exceptionally high quality.

Smart Cut is Soitec’s proprietary wafer bonding and layer transfer technology used to produce engineered substrates like SOI (silicon-on-insulator). It works by implanting hydrogen ions into a donor wafer, bonding it to a handle wafer, and then splitting off a thin active layer. The remaining donor wafer can be reused, enhancing cost efficiency. This enables precise control of layer thickness and uniformity, critical when designing and producing waveguides for photonics applications, with high performance and yield at scale.

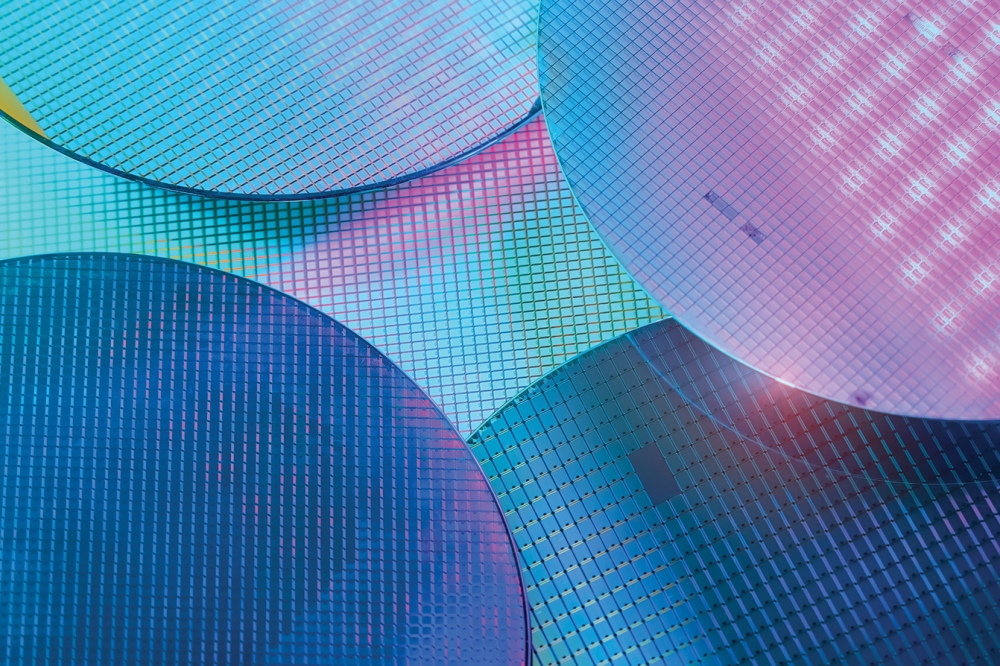

Figure 1. From pluggable optics to CPOs & OIOs.

Soitec’s Photonics-SOI substrates are specifically engineered with a top mono-crystalline silicon layer (“device layer”) with precise thickness control, commonly about 220 nm or 340 nm. Below this top layer, the substrates have a buried oxide layer (“BOX”) of optimised thickness (typically 2–3 µm) critical for optimal fibre edge coupling, and a low-defect and high-uniformity silicon base wafer. This layered structure, illustrated in Figure 3, is critical for defining single-mode waveguides with high precision, essential for dense, low-crosstalk optical routing.

Additionally, the large refractive index contrast between top silicon (typically about 3.48) and silicon dioxide “BOX” (typically about 1.44) in the SOI stack provides strong optical confinement. This minimises mode spreading, enables small bending radii, supporting compact layouts, and facilitates high-density photonic integration (critical in transceivers, switches, and CPO architectures).

Finally, low optical propagation loss is ensured thanks to ultra-smooth silicon surfaces and interfaces. This is essential for minimising scattering loss in waveguides, ensuring <1 dB/cm propagation losses in optimised designs, and supporting high-Q resonators and interferometers with minimal insertion loss.

Thanks to the advantages outlined above, Soitec’s substrates are used by leading integrated photonics designers and system providers, bridging semiconductor and photonic ecosystems. This in turn underpins the adoption of silicon photonics in real-world applications, which is already happening in AI supercomputing clusters and optical I/O for accelerators.

Figure 2. Layered structure of a photonics-SOI substrate.

Vision for the future

The exponential growth of AI, particularly in the cloud, demands an equally transformative shift in how data moves. This will only be compounded as AI evolves toward real-time reasoning, edge-to-cloud learning loops, and trillion-parameter models.

Providing the essential ingredients of speed, efficiency, and integration, silicon photonics will become a non-negotiable foundation for performance and sustainability, overcoming the limitations of electrical interconnects.

In the coming years, we expect to see the mass adoption of CPO in hyperscale environments, new hybrid compute-photonic architectures, and photonic AI chips using light for both communication and computation. Soitec’s contributions at the materials level are pivotal. By providing substrates optimised for optical performance and semiconductor integration, Soitec ensures that the promise of silicon photonics can scale globally and reliably.

Adding to this roadmap, Soitec is preparing to launch lithium niobate on insulator (also called LNOI and TFLN) – a new engineered substrate platform aimed at unlocking ultra-fast, low-loss electro-optic modulation and nonlinear photonic functions. LNOI will be targeting high-speed modulators starting at 1.6T (200G per lane) with main adoption planned for 3.2T (400G per lane), driven by superior modulation bandwidth and ultra-low drive voltage compared to incumbent technologies. The possibility of hybrid and heterogenous integrations with silicon photonics will make Soitec’s LNOI platform a real boon to integrated photonics adoption.

This innovation signals an even broader vision: a heterogeneous photonics future where multiple materials and functions are integrated at the wafer level to meet the demands of AI, quantum computing, and next-generation communications. With its growing portfolio of advanced materials, Soitec is not just supporting the evolution of silicon photonics but actively shaping the future of optical technologies. The future of cloud AI is bright – literally – and it’s being realised, in part, by the photons travelling through Soitec’s engineered substrates!