Intel reveals fully integrated optical I/O chiplet

The company describes its optical compute interconnect chiplet as a revolutionary milestone in integrated photonics technology for high-speed data transmission

At the Optical Fiber Communication Conference (OFC) 2024, Intel’s Integrated Photonics Solutions (IPS) Group demonstrated what the company describes as the industry’s most advanced and first-ever fully integrated optical compute interconnect (OCI) chiplet co-packaged with an Intel CPU and running live data. Intel says its OCI chiplet represents a leap forward in high-bandwidth interconnect by enabling co-packaged optical input/output (I/O) in emerging AI infrastructure for datacentres and high performance computing (HPC) applications.

The OCI chiplet is designed to support 64 channels of 32G data transmission in each direction on up to 100 metres of fibre optics and Intel expects it to address AI infrastructure’s growing demands for higher bandwidth, lower power consumption, and longer reach. The company says it enables future scalability of CPU/GPU cluster connectivity and novel compute architectures, including coherent memory expansion and resource disaggregation.

AI-based applications are increasingly deployed globally, and recent developments in large language models (LLM) and generative AI are accelerating that trend. Larger and more efficient machine learning (ML) models will play a key role in addressing the emerging requirements of AI acceleration workloads. The need to scale future computing platforms for AI is driving exponential growth in I/O bandwidth and longer reach to support larger processing unit (CPU/GPU/IPU) clusters and architectures with more efficient resource utilisation, such as xPU disaggregation and memory pooling.

Electrical I/O (i.e., copper trace connectivity) supports high bandwidth density and low power, but only offers short reaches of about one metre or less. Pluggable optical transceiver modules used in datacentres and early AI clusters can increase reach at cost and power levels that are not sustainable with the scaling requirements of AI workloads. According to Intel, a co-packaged xPU optical I/O solution can support higher bandwidths with improved power efficiency, low latency and longer reach – exactly what AI/ML infrastructure scaling requires.

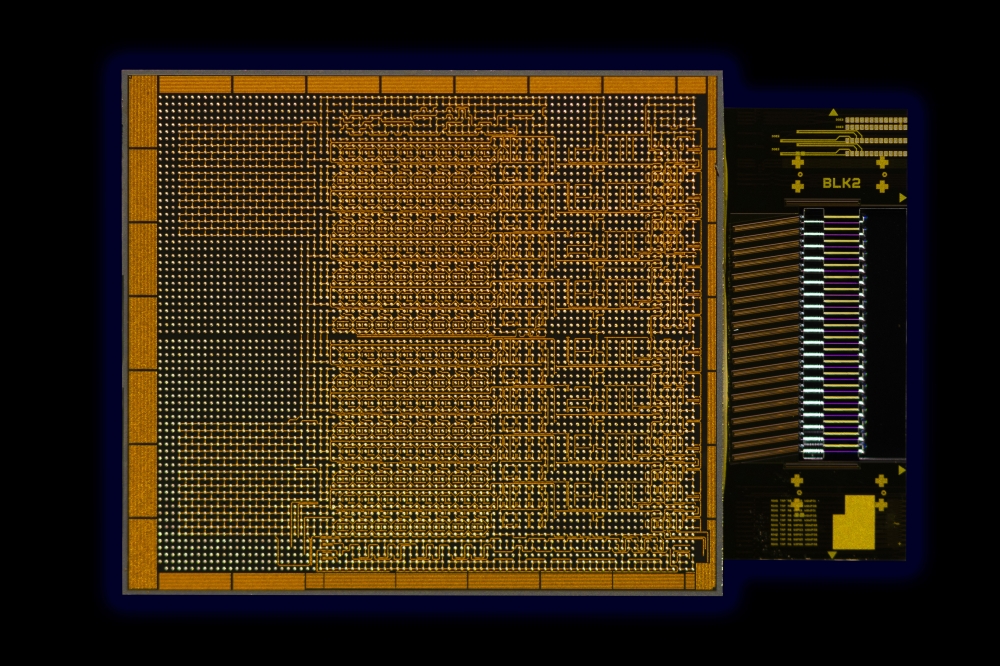

The company says its fully Integrated OCI chiplet leverages its field-proven silicon photonics technology and integrates a silicon PIC, which includes on-chip lasers and optical amplifiers, with an electrical IC. The OCI chiplet demonstrated at OFC was co-packaged with an Intel CPU but can also be integrated with next-generation CPUs, GPUs, IPUs and other system-on-chips (SoCs).

According to Intel, this first OCI implementation supports up to 4T bidirectional data transfer, compatible with peripheral component interconnect express (PCIe) Gen5, while the live optical link demonstration showcases a transmitter (Tx) and receiver (Rx) connection between two CPU platforms over a single-mode fibre (SMF) patch cord. The company adds that the CPUs generated and measured the optical Bit Error Rate (BER), and the demo showcases the Tx optical spectrum with eight wavelengths at 200 GHz spacing on a single fibre, along with a 32G Tx eye diagram illustrating strong signal quality.

The current chiplet supports 64 channels of 32G data in each direction up to 100 metres (though practical applications may be limited to tens of metres due to time-of-flight latency), utilising eight fibre pairs, each carrying eight DWDM wavelengths, says Intel. The co-packaged solution is also highly energy efficient, consuming only 5 pJ/bit compared to pluggable optical transceiver modules at about 15 pJ/bit, adds the company.

Intel says its main differentiator is unparalleled integration using hybrid laser-on-wafer technology and direct integration, yielding higher reliability and lower costs, and allowing the company to deliver superior performance while maintaining efficiency. Intel adds that its robust, high-volume platform boasts shipping over 8 million PICs with over 32 million integrated on-chip lasers, showing a laser failures-in-time (FIT) rate of less than 0.1. These PICs were packaged in pluggable transceiver modules, deployed in datacentre networks for 100G, 200G, and 400G applications.

Next-generation, 200G/lane PICs to support emerging 800G and 1.6T applications are under development. Intel also says it is implementing a new silicon photonics fab process node with state-of-the-art device performance, higher density, better coupling and vastly improved economics. The company adds that it continues to make advancements in on-chip laser and SOA performance, cost, and power.

Intel’s current OCI chiplet is a prototype, and the company is working with select customers to co-package OCI with their SOCs as an optical I/O solution.

Image credit: Intel Corporation