Avicena showcases compact 1Tbps optical transceiver at SuperComputing 2023

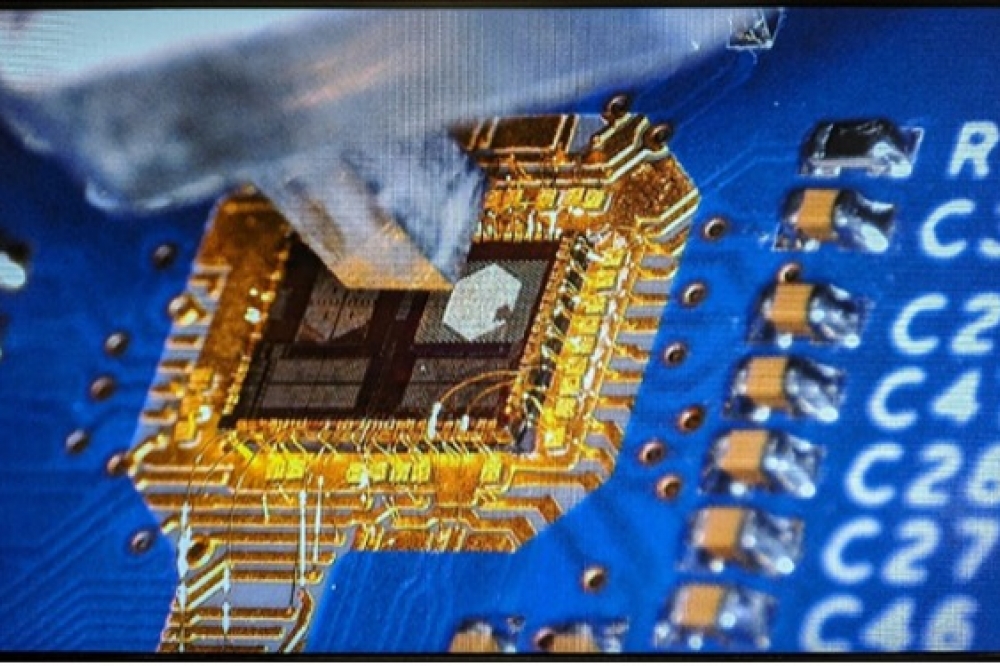

Avicena, a company developing optical links based on microLEDs is demonstrating what it says is the world’s smallest 1Tbps optical transceiver at the SuperComputing Conference being held from 12-17 November in Denver. The transceiver is being demonstrated as part of its LightBundle multi-Tbps chip-to-chip interconnect technology. The company says its microLED-based LightBundle architecture supports unprecedented throughput, shoreline density and low power, unlocking the performance of processors, memory, and sensors.

Artificial intelligence (AI) is driving an unprecedented surge in demand for compute and memory performance, driven by applications like ChatGPT based on large language models (LLMs). These sophisticated models have an insatiable appetite for computing power and fast access to large amounts of memory, resulting in an urgent and growing demand for much higher density low-power interconnects between Graphics Processing Units (GPUs) and high-bandwidth memory (HBM) modules.

Today, HBM modules must be co-packaged with GPUs because the GPU-memory electrical interconnect is limited to just a few millimetres in length. Subsequent HBM generations will require IC shoreline densities in the range of 10 Tbps/mm or more. According to Avicena, conventional optical interconnects based on VCSELs or silicon photonics (SiPh) promise to extend the interconnect reach but struggle to meet requirements in terms of size, bandwidth density, power, latency, operating temperature, and cost. By contrast, the company says its microLED-based LightBundle interconnects provide higher bandwidth density, much smaller size, much lower power and latency, and very low costs.

"At Avicena we are excited to showcase the world’s most compact 1 Tbps transceiver in the shape of a 3 mm x 4 mm CMOS ASIC using our patented microLED optical interface," says Bardia Pezeshki, founder and CEO of Avicena. "Everyone is talking about SiPh solutions for applications in AI clusters. However, for short reach interconnects with less than 10 m reach, we believe that our LED based solution is inherently better suited because the compact size, higher bandwidth density, lower power and latency, and temperature tolerance up to 150 °C."

Marco Chisari, head of the Semiconductor Innovation Center of Samsung, one of Avicena’s key investors, added: "Optical interconnect technology has the potential to improve chip-to-chip and inter-rack performance. With a roadmap to multi-Tbps capacity and sub-pJ/bit power efficiency, Avicena’s innovative LightBundle interconnects can enable the next era of AI innovation, paving the way for even more capable models and a wide range of AI applications that will shape the future."