Automation: an essential tool for testing Photonic Integrated Circuits

As Photonic Integrated Circuits (PICs) are more widely adopted in

component design and manufacturing, addressing the need for scalability,

speed and reliability of testing are emerging as keys to optimizing the

value of PICs in everything from telecommunications to LiDARS and

biosensing technologies.

By: Francois Couny, Ph.D., Senior Product Line

Manager, EXFO

The Photonic Integrated Circuits (PIC) testing ecosystem is comprised of both hardware and software solutions that have been evolving rapidly to meet the expanding needs of PIC scientists and technicians in labs and production facilities. But because foundries and labs need tests that can be reliably replicated and, in many cases, expanded to support mass production, automated processes are becoming more important than ever to support PIC testing. In this article we’ll look at the challenges labs and foundries typically face when looking for accurate, agile component testing, and how automation can help elevate testing to the next level.

Hardware challenges

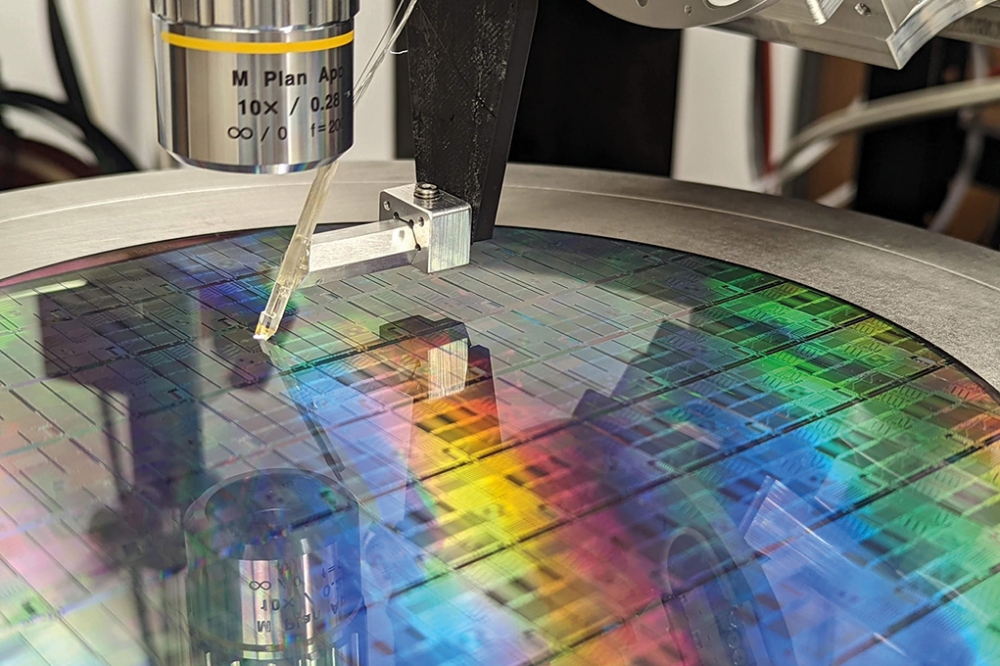

In the photonic component testing field, the industry has collectively applied creative thinking to use hardware to deliver new, more optimized test approaches. An excellent example of this is edge coupling at the wafer scale.

Generally, chips are designed such that a given circuit makes use of edge and surface couplers. While surface coupling enables light coupling into a device from the top surface – which is ideal when testing a wafer -- the final diced chip is often designed to use edge couplers. In these cases, the purpose of the surface coupler is merely to provide an interface for screening and early testing, enabling the die to be qualified as early as possible in the process. That is then followed by the edge coupler which is later used as a production interface.

One single software platform enabling preparation, execution, and analysis is key to scaling up production in a PIC ecosystem.

However, that has inherent problems because partial screening using a surface coupler can leave unchecked some problems arising from the untested section (the edge coupler section). An inadequate testing solution consists of designing optical “taps” on the component being tested, to serve both surface and edge-couplers. Such a design can have detrimental effects on chip performance, resulting in less efficient and more costly production chains.

This kind of hardware problem needs to be solved from the test station viewpoint by providing a set of hardware probe systems that deliver the agility and reliability required while ensuring speed and accuracy in all test conditions. Stations of that type available from EXFO can be reconfigured quickly to accommodate a variety of optical probes and PICs of different sizes and scope, while making use of different coupling methods. Ultimately, this comprehensive, automated solution ensures that testing can be optimized and replicated throughout the PIC production chain.

But the challenges don’t stop with coupling light in and out of the PIC device. Optical testing of components is often demanding due to the possible high port count of some components like arrayed waveguide grating (AWG) or the sheer number of components to test on a single die. EXFO has been leading the charge on PIC testing for some time and has advanced the industry with a component test platform designed to tackle multiport detection on complex devices.

Directly controlling one or several continuously tunable lasers, the instrument measures --quickly and with high fidelity -- insertion loss, return loss and polarization-dependent loss across the laser’s spectral range. With its modular approach and SCPI commands for automation, EXFO’s CTP10 overcomes test challenges on the hardware side by increasing PIC testing throughput while reducing test time.

It's important to note that in a PIC ecosystem where complex tests must be programmed, hardware and software must operate in symbiosis to ensure effective PIC characterization. Clearly, automation is not only critical for chip & test preparation and execution, and for data analysis and reporting, but it is also a cornerstone for hardware setup and calibration.

A key challenge regarding configuring PIC testing is tracking and documenting successful test configurations so they can be correlated, replicated, and adopted within a lab or production facility. Furthermore, testing elicits lots of data that must be properly tracked and analyzed so testing can be optimized to meet new requirements.

Every PIC facility has experienced setting up test configurations using home-grown test processes and methods, and been challenged when trying to draw on broader industry insights. Frequently, full visibility of what is being done and archived is simply not obtainable using in-house software, weakening any actionable data obtained from testing.

Because of the extensive manual effort required and the high volume of chips, some R&D prototyping only involves fully and extensively testing a small percentage of available chips. Tracking data and being able to analyze outcomes, as to whether a trend was emerging or whether one-off situations were occurring, was nearly impossible. In-house automation solutions generally lead to data that is not statistically significant, another negative impact on the usability of the data.

One additional challenge to address is test reach. Fast and easy to implement, simple testing involving insertion loss using only a photo detector is too limited to grasp the full picture of why and how a particular chip fails and what actions to take to remedy it. Clearly, manual and in-house automated testing can only take things so far in the PIC development process because of the inability to scale up, replicate, and completely control tests -- and because operation is based on a mere subset of what’s possible to test and analyze.

PIC testing requires a set of state-of-the-art equipment operating in symbiosis to achieve maximum yield.

Automation to support a burgeoning industry

As noted earlier, software automation in PIC testing is critical for the industry to respond to the rapid expansion in use of PICs in multiple markets and in high-volume manufacturing.

When introducing automation, it forces decision-making on what’s important to test and what information is critical to track. An up-front assessment can help ascertain if current testing is useful or whether new test methods are needed. The ability to use software algorithms to extract more information from available data is highly valuable.

Automating the existing test bench means that optical aligners can be motorized to streamline test processes. While test capacity can be as much as doubled, testing configurations can either cover more ground, giving an exhaustive view of the chips under test, or reduced to a few performance checks for more cost-effective and nimble production.

Another advantage of a fully-automated system is the complete autonomous testing that can yield in-depth test analysis. As such, labs and foundries are no longer limited to creating “gaussian curve” statistics but are empowered to understand the root cause of anomalies and what to do to resolve them. Test summary dashboards, populated automatically, provide the right information to the right people at the right time for best decision-making.

Instead of a tedious manual process, automated testing, analysis, and reporting are streamlined, resulting in better specifications, fewer iterations to optimization and a better overall finished product and production. As a result, PIC chips are cheaper to develop, cheaper to produce and have a faster time-to-market, ready for mass production.

Industry advances in automation: EXFO acquires EHVA to accelerate PIC testing

EXFO has worked over the years to develop test and measurement hardware and software solutions that are automated, scalable, fast, accurate and cost-optimized. These solutions range from simple optical testing to spectral optical characterization or traffic analysis, and they have proven interoperability with third-party instrumentation such as wafer disc handling systems.

To further accelerate EXFO’s innovation engine in PIC testing, in 2022 EXFO acquired EHVA, an innovative maker of test and measurement systems for PICs and system automation. Developed by PIC engineers for PIC engineers, EHVA’s expertise in manufacturing intelligence and wafer-to-single device test capabilities through their scalable PIC testing solutions enabled faster component manufacturing and better reliability of production processes. This resulted in a series of advanced test stations that are reconfigurable from single-die test to 300mm wafer, offering flexible testing of surface and/or edge coupling PICs with DC and RF test capabilities.

Now part of the EXFO portfolio, EHVA’s process software suite, integrating advanced test systems such as the CTP10, can be implemented in customer lab and manufacturing settings for exceptional testing reliability and efficiency; a fully automated solution that can help avoid production bottlenecks.

Together with world-class photonics industry leaders, EXFO works toward testing standardization and looks forward to developing many new innovations to address the growing PIC market.

Future opportunities based on automation

As with all evolutionary technologies, some innovations are more impactful than others. The ability to scale testing to support PIC technology is the next gamechanger. Automated testing is already critical for telecommunications with the advent of PIC-based transceivers, but it also holds major promise for LiDARS, quantum computing/sensing/encryption, biosensing, high-performance AI, and more. Some of those applications are even more sensitive and require much higher specifications or much lower tolerances than components seen in telecom applications.

The importance of PIC technology cannot be underestimated, given it is expected to be the backbone for most future key innovations. Testing complex AI chips, quantum chips and more will be required in future, and today’s PIC testing is laying the foundation for those evolutionary – and revolutionary – technologies. And none of that can happen without the underpinning of automated processes now available for PIC testing with scalability, reliability, and speed.

For more on PIC testing from EXFO, visit https://www.exfo.com/en/solutions/academic-research-institutions/pic-testing