Simulations evaluate variations in PIC manufacturing

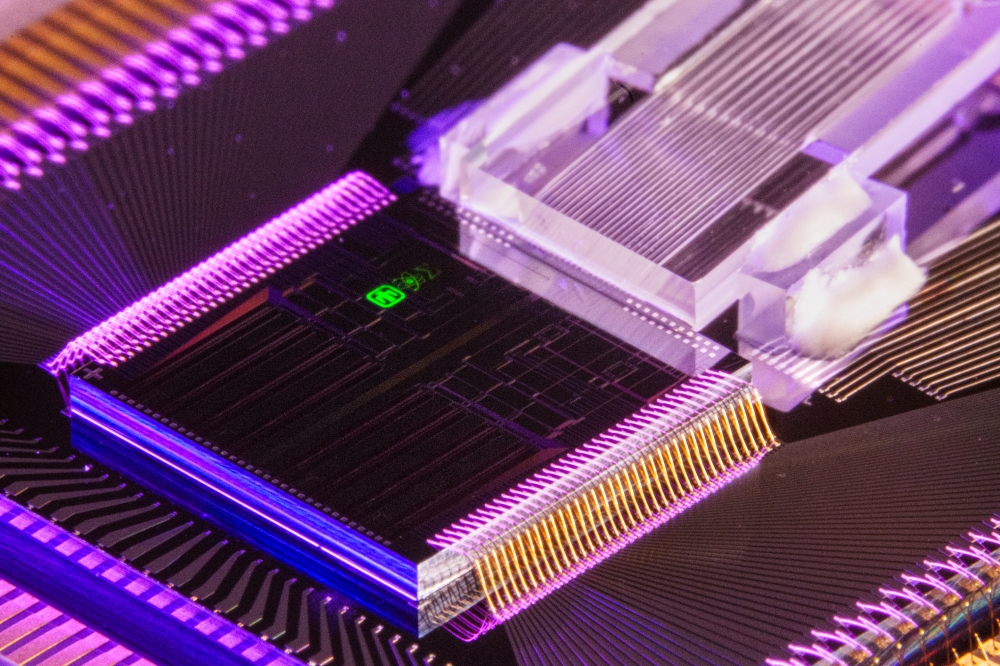

Academia and industry join forces to tackle two challenges of photonic integrated circuit (PIC) design: characterizing manufacturing variations and predicting their influence on circuit performance.

By James Tyrrell

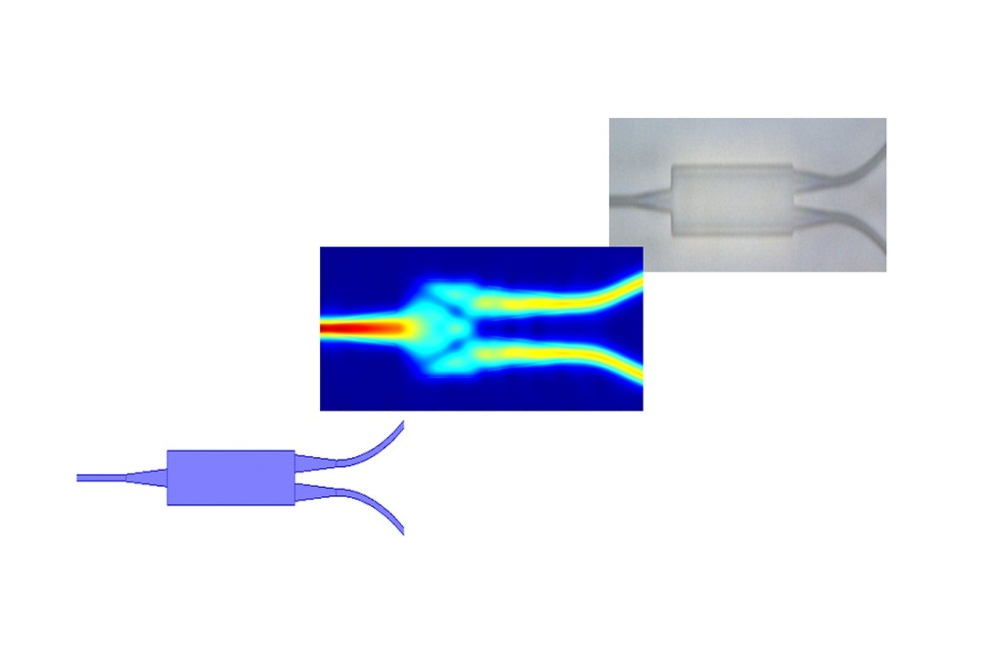

Researchers based at the University of British Columbia together with engineers from Lumerical Solutions have developed an enhanced Monte Carlo (MC) simulation methodology to predict the impacts of layout-dependent correlated manufacturing variations on the performance of photonics integrated circuits (PICs).

"Typically, a digital circuit will work if all of its components operate properly. However, most photonic designs are analog circuits; as a result, photonics yield analysis is based on circuit performance rather than single device performance, which is similar to that of analog electronics," comments the team.

Reporting its results in the journal Optics Express, the group tackles two challenges of PIC designs: characterizing manufacturing variations and predicting circuit performance under the impacts of correlated manufacturing variations.

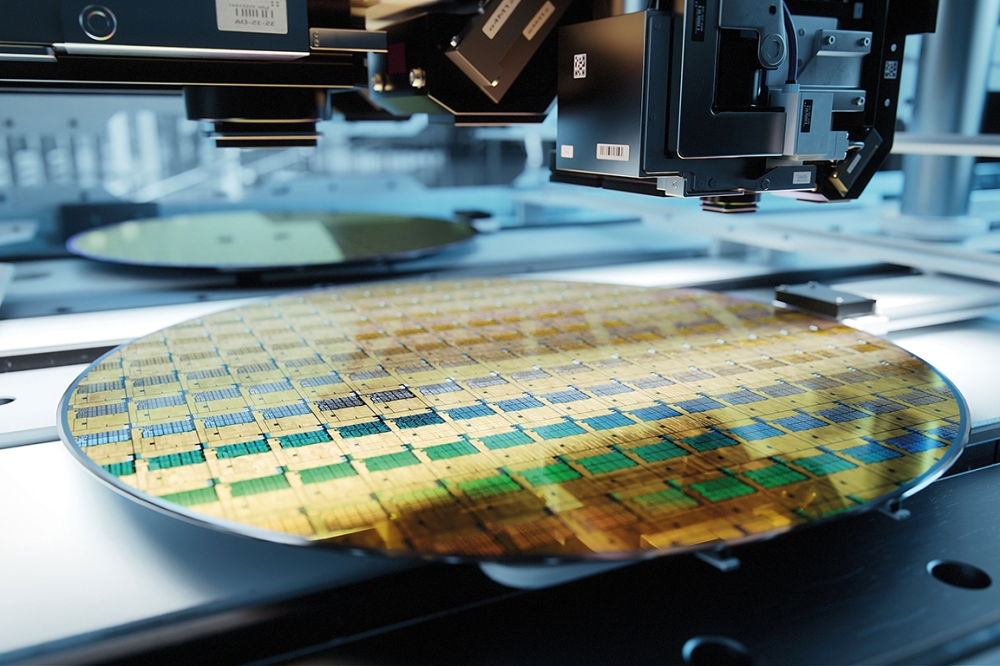

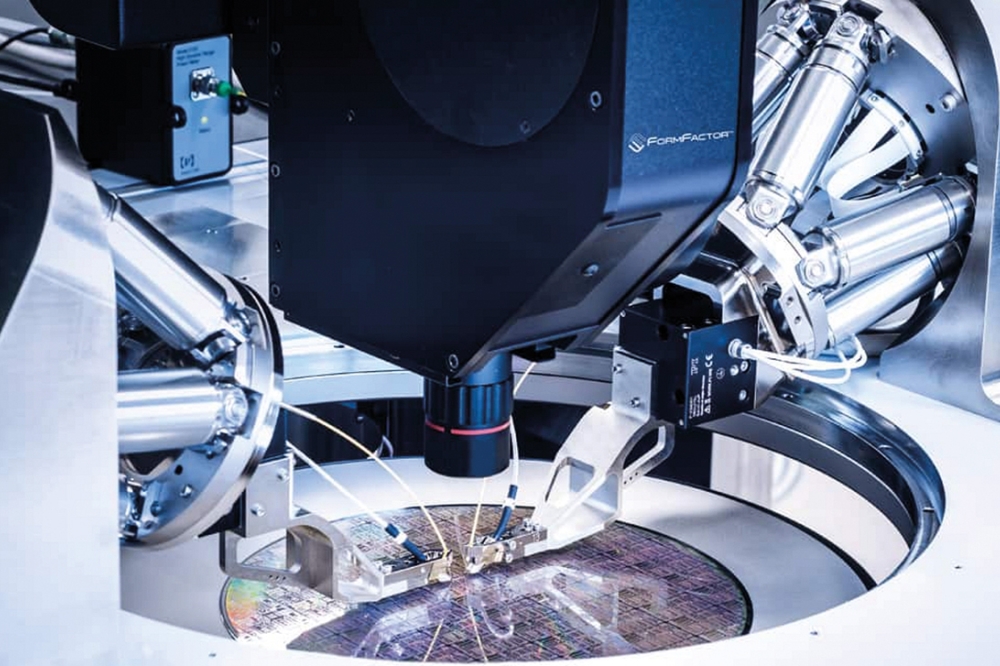

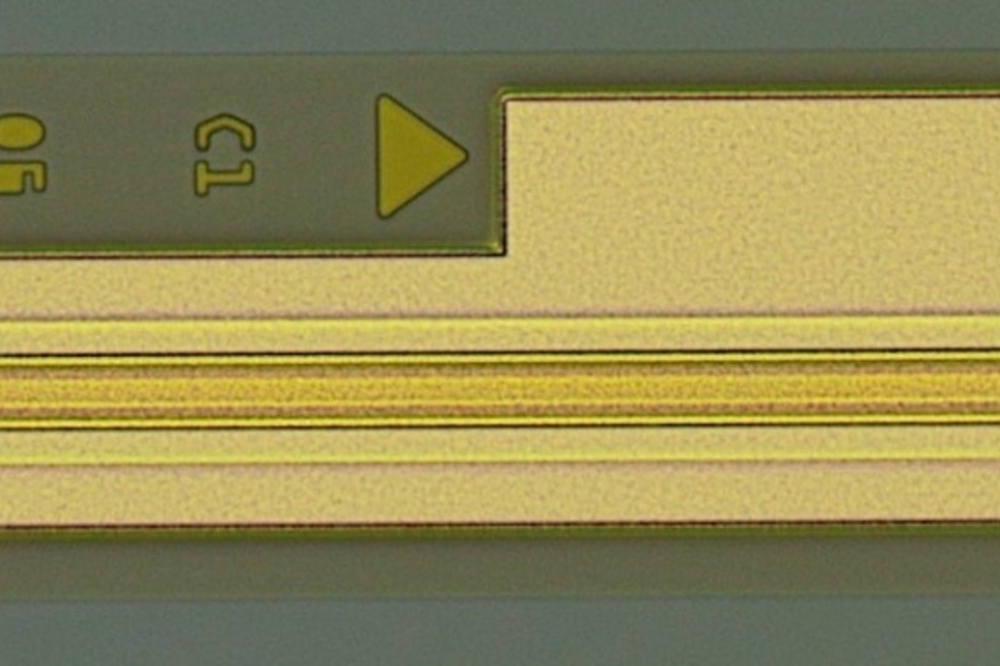

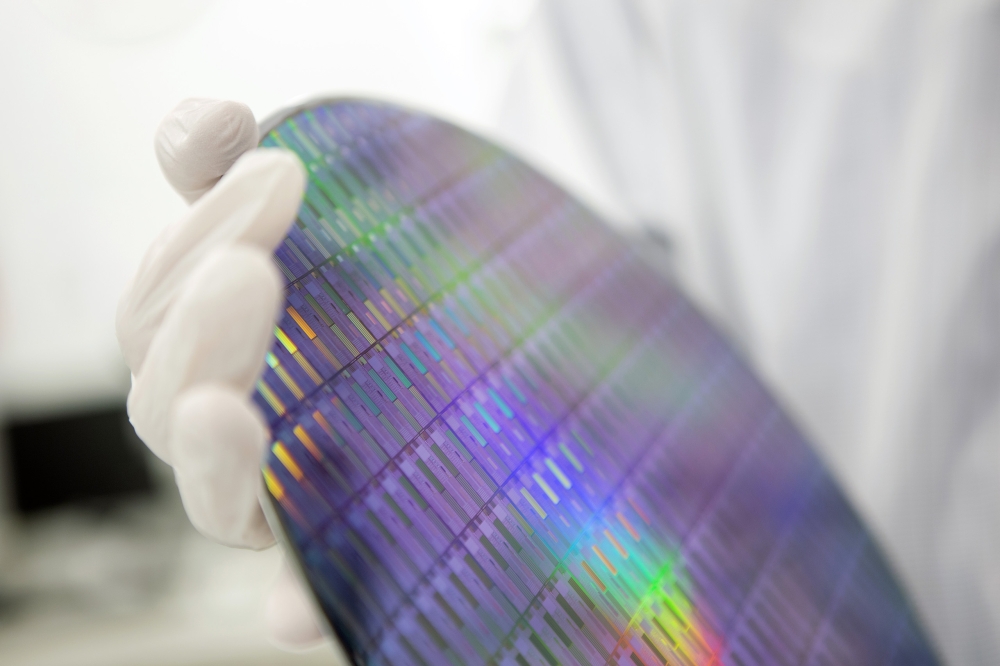

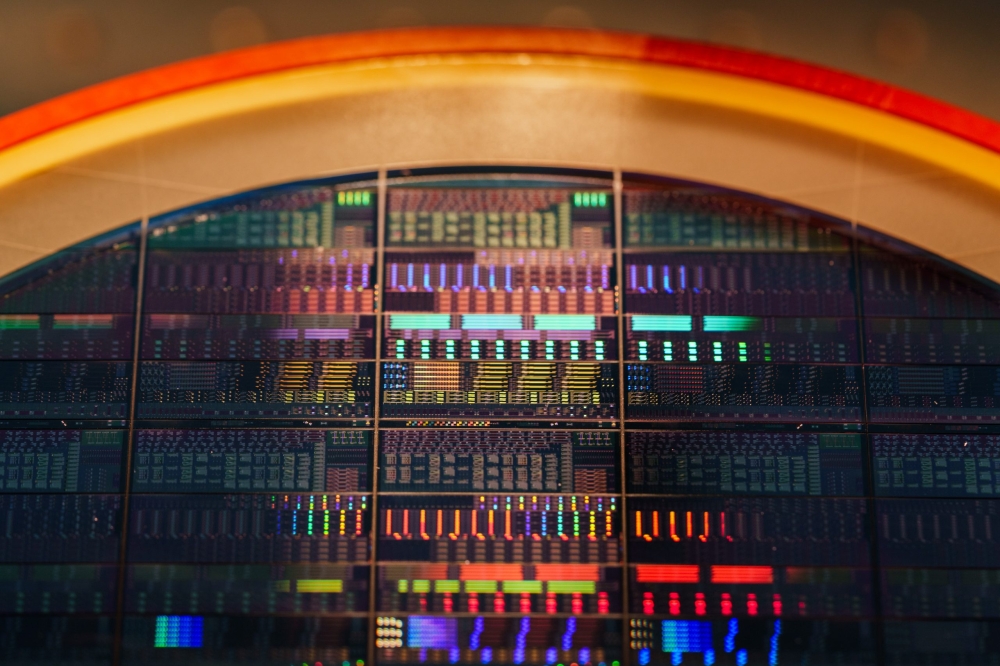

"We have demonstrated a simple and accurate characterization method for the manufacturing variations of PICs, which extracts the waveguide width and height from the spectral response of a single racetrack resonator," write the authors in their paper. "Using this method, we have measured the spectral responses of 2074 identical racetrack resonators on a 200-mm-wafer that was fabricated through a 248-nm DUV lithography photonics process, and we extracted the waveguide width and height at each device location on the wafer."

The team then fed this information into simulation flows and models to predict the performance of PICs under the impact of correlated manufacturing variations.

Reference -

Opt. Express 25 9712-9733 (2017) [open access]