PIC Design: schematic or layout first? Both!

André Richter, Sergei Mingaleev and Igor Koltchanov of VPI Photonics discuss the power of a layout-aware schematic-driven design methodology for accelerating the application of integrated photonics.

Motivation

Despite impressive advances in integrated photonics technologies, costs associated with the design and fabrication of photonic integrated circuits (PICs) are still several orders of magnitude higher than those for their microelectronic counterparts, which limits the rapid application of PICs in many areas. The need to reduce these costs has been a major driving force for integrated photonics development during the past few years. So why not directly adopt the well-proven methodologies from electronic design automation (EDA)? While similar to electronics, the key for cost reduction lies in the introduction of standardized process design kits (PDKs) and a generic foundry model. However, recent design trends show that dedicated photonic design automation (PDA) tools "“ closely integrated with EDA tools "“ are necessary to address the specific PIC design needs.

The fundamental difference between the design processes for photonics and electronics is caused by the double nature of optical waveguides. In some cases, they just route optical signals between building blocks (BBs), comparable to electrical wires in electronic circuits. This is when waveguide properties might not be important. In other cases, however, waveguides determine interference conditions between signals in different optical paths. Their properties are of crucial importance in such cases and should be known and already taken into account at the start of the circuit design. Unfortunately, there is no clear separation between those two types of cases. As the designed PIC grows, adding new couplers between reflective parts may turn any connecting waveguide into a functional one. Functional waveguides often serve as connectors of other components, so their dimensions are restricted not only by the desired functions, but also by the geometrical requirements of an adequate layout connectivity. Consequently, the PIC design process cannot be separated so easily into two distinct stages as is possible in the case of electronic circuit design. This is outlined in more detail below.

Utilizing the standard schematic-driven design approach, the circuit layout is fully determined by the connectivity between ports of neighboring PDK BBs, which requires that the layout of any individual BB is completely defined by its parameters. This allows circuit simulations of the designed PIC to be performed immediately, since the compact simulation model of each BB is known at any design step. However, due to the twofold nature of optical waveguides in PICs this approach is often not feasible. For instance, even the design of a simple Mach-Zehnder Interferometer (MZI) with a given free-spectral range (FSR) around a nominal center frequency sets a number of functional and geometrical design requirements on the two optical waveguide arms forming the MZI, which leads to deriving and solving a cumbersome set of nonlinear equations. In practice, attempts to design more or less complex PICs employing the standard schematic-driven design approach can result in very time-consuming back and forth iterations between the circuit simulator and layout tool. Moreover, design tasks such as device performance and yield optimization cannot be automated and thus become merely unmanageable.

For a number of applications, the problems outlined above can be solved by employing a layout-driven design approach. For example, dedicated photonic layout design tools (such as OptoDesigner by PhoeniX Software and IPKISS by Luceda) provide advanced scripting capabilities with support of an easy netlist-based PIC design process and immediate access to relative and absolute locations of any BB ports inside the circuit netlist. Moreover, they provide advanced routing capabilities, including support of elastic waveguide connectors. However, accurate and efficient simulation of modern large-scale PICs with a mix of passive and active BBs requires development of complex specialized circuit simulation engines. That is why the layout-driven design approach should include a separate stage for the simulation of the designed PIC with a dedicated photonic circuit simulator. But simulations of complex non-passive circuits require embedding the designed PIC into a complex simulation framework: adding properly configured electrical and optical sources, post-processing of output signals with specialized instrumentation tools, and visualization of obtained results. Consequently, designers need again to frequently switch between a layout design tool and circuit simulator, and experience serious difficulties trying to organize automated sweeps over layout parameters or perform automated design optimization.

Layout-aware schematic-driven design methodology

The layout-aware schematic-driven design methodology [1] represents an efficient practical solution to the issues outlined above, as it allows circuit simulation and layout design tasks to be performed simultaneously, using the same schematic capture environment. For this, a circuit-level simulator is seamlessly integrated with a layout design tool, providing designers transparent access to the capabilities of both software packages, as illustrated in Fig. 1. In particular, it becomes possible to directly specify in the circuit-level simulator physical locations and orientations of PDK BBs on the final layout. Also, the library of PDK BBs is extended with a set of elastic waveguide connectors (the same as provided by the underlying layout design tool), allowing sub-circuits having fixed locations to be easily interconnected without the need to manually solve complex geometrical problems. The circuit simulator automatically, and invisibly for users, invokes the layout design tool to determine the actual physical lengths and shapes of all elastic connectors, constructs compact simulation models for them, and after that initiates the circuit simulations. This allows the combination of graphical schematic capture, layout design with automated waveguide routing, and circuit simulations, which are currently considered separately representing a major problem for PIC designers.

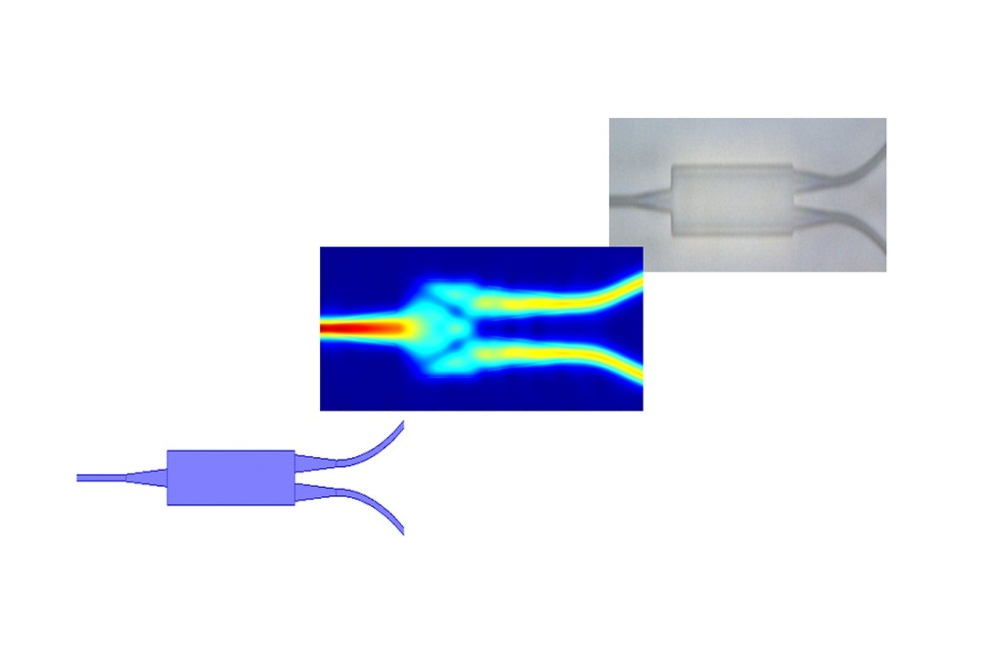

As an illustration of this design workflow, let us consider the MZI design shown in Fig. 2. Problematic waveguides use elastic waveguide connectors; the physical locations and orientations of all outer waveguides are directly specified with absolute coordinates, allowing packaging requirements to be fulfilled. Finally, the physical location and orientation of the MZI sub-circuit can be specified using relative coordinates with respect to the location of the port of another block with fixed location. All of these port locations can be specified using advanced parameter scripts "“ so that, if required, locations of BBs can be specified after solving arbitrarily complex equations. That is, the circuit may now be designed in almost the same way as it would be designed with the layout-driven approach. Since this design is still performed in a circuit simulator environment, one can easily combine PDK BBs with any signal sources and instrumentation modules required for signal post-processing and organization of parameter sweeps and/or optimization.

Figure 1. Layout-aware schematic-driven design methodology enabling transparent access to information and functions in both domains

Here, the Spectrum Analysis block allows transfer function spectra to be visualized, automatically extract their peak properties, and estimate and plot the device FSR. Importantly, our implementation of the layout-aware schematic-driven design approach supports automated sweeps and optimization of layout parameters. For this, the layout design tool is automatically invoked to determine the actual physical lengths and shapes of all elastic connectors at each simulation step. As an example, Fig. 2 (bottom, left) shows the dependence of MZI FSR on the bend radius R as result of an automated parameter sweep, which can be easily organized by the PIC designer by merely specifying the name and value range of the swept parameter. Also Fig. 2 (bottom, right) illustrates automated optimization of the same bend radius for a desired FSR of 200GHz. Other frequently required simulation capabilities, such as multi-dimensional parameter sweeps and optimization, combination of sweeps with optimization, sensitivity and yield analysis, as well as yield optimization can be supported with this approach as well.

In practice, the PIC design usually starts with elaborating a circuit idea "“ at this stage, the circuit layout is ignored, and designers concentrate on elaborating a principal scheme which enables the required circuit functionality. This stage can be addressed by a standard schematic-driven design methodology, based on the usage of standard PDK waveguides. At the second stage, the circuit layout is taken into account ensuring layout connectivity and accounting for packaging requirements. To simplify the transition from the first to the second stage, we provide the possibility to easily replace all selected standard waveguides with their elastic counterparts, and thus introducing layout flexibility which is used to optimize the circuit design and easily satisfy all packaging requirements. This is the stage where the layout-aware schematic-driven approach is most intensively used. Once the optimal circuit design is fully elaborated, it may be a good idea to "fix" its layout. For this, we provide the possibility to easily replace elastic waveguide connectors with their standard counterparts, fully preserving the optimal circuit layout. Such a circuit may now be automatically converted into a compound building block and be used as part of a more complex circuit.

Figure 2. Circuit schematic of MZI design in VPIcomponentMaker Photonic Circuits (top). Physical dimensions of elastic connectors and port locations are resolved by automatic silent operation of OptoDesigner. Advanced instrumentation enables automated signal post-processing, such as automated sweep or optimization to detect the dependence of FSR on waveguide bend radius (bottom).

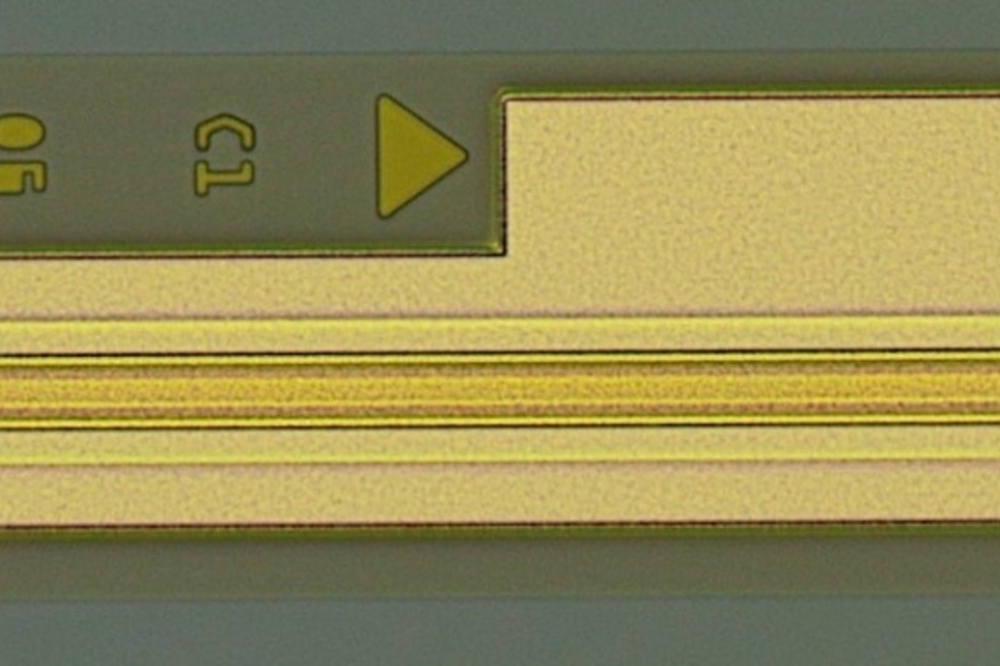

Similar to electronics, the design of large-scale PICs requires splitting the whole circuit into manageable functional sub-circuits, which are possibly further decomposed into yet smaller sub-circuits and foundry-certified PDK BBs. Support of this type of multi-level hierarchy within the framework of the layout-aware schematic-driven methodology is non-trivial. Considering the design example of a cascaded-MZI demultiplexer in Fig. 3, the input optical signal is split between two cascaded MZIs, both being instances of the same user-defined parameterized compound BB CascadedMZI with only different parameter settings. The CascadedMZI block contains, in its turn, three instances of another compound BB MZI, built of fundamental PDK BBs and elastic connectors. Importantly, user-defined compound building blocks need to support the same design workflow as built-in PDK BBs. That is, they should offer the possibility to specify physical locations and orientations of their ports on the final layout. In our example, this mechanism is used to specify locations of the CascadedMZI blocks. Another important functionality is the possibility to create custom compound BBs that are described by functional design parameters rather than structural layout parameters. In the case of the MZI block in Fig. 3, we employ FSR and resonance frequency instead of specifying waveguide lengths and bend angles. This requires parameter scripting [2] enabling calculation of the needed waveguide dimensions by solving a system of nonlinear equations derived from a maximally compact layout condition enabling the desired FSR and resonance frequency.

As discussed above, handling the complexity of large-scale PIC designs requires the use of a layout-aware (multi-level) hierarchical methodology. However, this alone is not always sufficient "“ especially in applications addressing the design of large-scale optical networks on chip (NoC), as illustrated in Fig. 4. The major problem in designing such networks is given by properly interconnecting all paths between the optical switches, including the resolution of waveguide crossings. An NxN switching network requires N2 interconnections, which may be organized in different ways: minimizing the total number of waveguide crossings (thus minimizing total optical power losses), or trying to balance the number of crossings for each optical path (thus balancing optical power losses). The optimum scheme depends on the optical properties of the underlying BBs (waveguide, bend, and crossing). Therefore, the analysis and optimization of such networks requires the construction and simulation of a large number of complex circuits.

Figure 3. Schematic of cascaded MZI in VPIcomponentMaker Photonic Circuits (top left) employing multi-level hierarchy (bottom).

The layout (top right) is exported through OptoDesigner.

Trying to construct such networks manually (dragging, dropping, and connecting hundreds of BBs) is an extremely inefficient and error-prone process. This problem can be solved by providing support through macro scripting capabilities, which permit the placing and connection of any BB on the schematic and the adjustment of its parameters in a programmatic way. VPIcomponentMaker Photonic Circuits supports macro scripting with Python and its very powerful object-oriented programming capabilities being extended by a library of special commands addressing almost any task that can be performed through the standard user interface. The successful design of complex optical networks as shown in Fig. 4 with macro scripting requires its extension with a set of layout-aware commands, which allow physical locations and orientations of BB ports to be determined on layout, locations of waveguide crossing, and others. Enabling such standard capabilities of layout design tools in circuit simulators represents another important reason for the close interfacing between circuit simulation and layout design tools.

Summary

The layout-aware schematic-driven PIC design methodology enables a smooth photonic circuit design workflow starting with a logical idea and allowing users to gradually elaborate (still staying with a circuit simulator) its layout at any desired level of details, easily incorporating requirements such as adequate layout connectivity, packaging, and functional specifications. This methodology is based on extending a circuit-level simulator with the capabilities of layout design tools, such as the capability to specify directly physical locations and orientations of PDK building blocks on the final layout and to connect sub-circuits having fixed locations by smart elastic optical connectors.

Figure 4. Large-scale optical interconnect switching network, designed using layout-aware macro scripting with VPIcomponentMaker Photonic Circuits (layout via export to OptoDesigner).

Consequently, graphical schematic capture and automated waveguide routing can be combined. Enabling this functionality: the circuit simulator automatically and invisibly for users invokes a layout design tool to determine the physical dimensions of elastic connectors, constructs compact simulation models for them, and initiates the circuit simulations. Importantly, the presented approach enables automated parameter sweeps and optimization even for parameters that affect the circuit layout "“ a task which cannot be performed by standard schematic-driven or layout-driven design approaches. Based on our experience, we predicate that, driven by the fundamental difference between electronic and photonic circuits, the future development of PDA tools will proceed further with much closer integration between circuit simulation and layout design tools than it was ever required for EDA tools.